网络技术在飞速的发展,网络接口的性能也在不断提高。由于以太网接口成本低,速度快,性能好,开发方便,越来越多的数据采集系统采用以太网接口作为最终的数据输出及控制端口。而在相应的嵌入式系统领域,越来越多的芯片,从单片机到DSP,也都逐渐开始支持以太网接口。TCP/IP协议是被广泛支持的以太网协议,在嵌入式系统中实现了TCP/IP协议,就可以方便地与计算机主机相连,将采集到的数据传输到主机进行保存和处理。

针对高速信号采集和处理系统,数据从采集-信号处理-网络传输,整个过程中一方面要保证信号处理的速度,即采集到的信号能够在限定的时间内得到处理,另一方面则要保证整条数据流通路不能有瓶颈。一般说来,网络接口由单独的芯片负责,才能保证其传输的实时性和高效率,而信号采集和处理则是另外的芯片负责。无论是AD与DSP之间还是DSP相互之间,都存在高速通信的问题。经过论证和实践,我们认为使用FIFO是很好的选择。

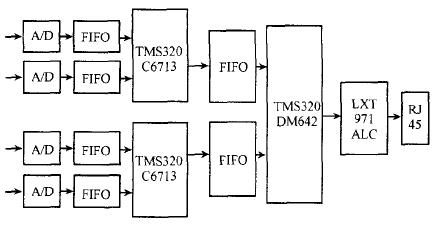

本文以TI(Texas Instruments)公司TMS320C6000系列芯片为基础,实现了一套高速信号处理—— 网络传输系统,如图1所示。高速A/D采集的数据通过FIFO(IDT72V273)传入TMS320C6713 DSP之中,该DSP芯片同步实时采集多路A/D数据并进行信号处理,由于传感器数目较多,我们采用了两片C6713同步处理的方式。两片C6713的处理结果通过各自后端的FIFO(IDT72V273)传入TMS320DM642 DSP。该DSP专用于数据的打包和网络发送。网络物理层由网络收发芯片LXT971ALC实现,最后数据通过网络进入计算机进行显示、保存和进一步处理。该系统实现了完整的传感器信号的高速信号处理、传输通路。技术上的难点除了信号处理算法之外,最主要的就是基于FIFO和网络的高速数据传输。本文根据在开发实践中积累的一些经验,对FIFO一网络数据传输的一些问题进行了探讨。

图1 信号处理-网络传输系统

1 硬件设计

在TI的C6000系列DSP中,C67x系列属于浮点DSP芯片,其中以C6713的运算能力最强,在300 MHz主频下,可达到2400 MIPs(百万指令每秒)和1800 Mfloot/s(百万浮点运算每秒)的运算速度,适合于大数据量和较复杂的浮点信号处理。而DM642作为定点DSP芯片,其主要优势不仅在于其速度快、性能好,还在于它自身携带了网络接口,硬件设计较为方便。

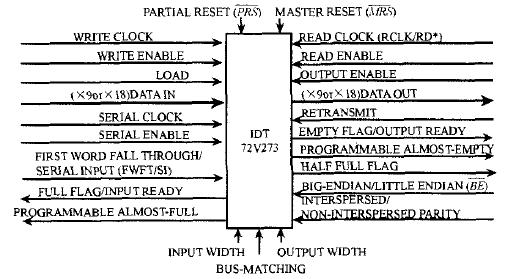

所谓FIFO,即“First In First Out”,是一种“先进先出”的存储器。FIFO存储器就像数据管道一样,数据从管道的一头流入、从另一头流出,先进入的数据先流出。以本文所采用的IDT72V273 FIFO芯片为例,其容量为16k×18或32k×9,主频达到133 MHz,仅6 ns读写周期,具有读指针和写指针,可以在FIFO出口读数据的同时在入口写入数据,能够满足实时系统的要求。本系统中在两处都用到了FIFO:A/D与C6713的数据接口及C6713和DM642的数据通道,FIFO基本接口如图2所示。

图2 FIFO 接口电路

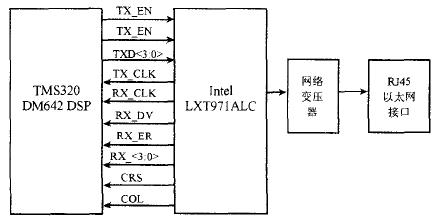

DM642自身带网络控制器EMAC,省去了购买或开发网络子卡的麻烦,在硬件上只需连接一个网络收发芯片Intel LXT971ALC 即可,如图3所示。

图3 DM642网路接口电路

2 软件设计

软件开发在TI的集成开发环境CCS(Code Composer Studio)中进行,TI给C60000系列DSP提供了稳定高效的DSP/BIOS操作系统,为了方便网络开发,还提供了网络开发套件NDK(Network Developer's Kit)。所有的这些,保证了用户可以使用标准的C语言(程序中对速度要求较高的部分也可以用汇编语言)完成整个应用程序的开发,对硬件的操作只需调用相应API函数即可。

2.1 软件流程

无论是C6713还是DM642,都需要对FIFO进行操作。C6713需要读取FIFO传过来的A/D信号,进行处理后将结果写入后端的FIFO。而DM642则读取C6713发来的FIFO数据,进行网络打包发送。FIFO数据的读取部分,对于两者都是一样的,C6713给后端FIFO存数据,也只需对相应地址写入即可,所以C6713的程序,算法以外的部分跟DM642有相似之处,且相对简单。本文着重讨论DM642的程序流程。

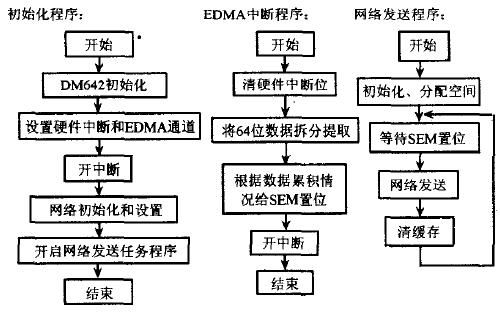

DM642与C6713读取FIFO数据时,都是以EDMA的方式进行的。EDMA控制器可以独立于CPU工作,从而可方便地实现片内存储器、片内外设以及外部存储空间之间的数据转移。由外部中断自动触发EDMA传输,可以大大提高传输速率和CPU的工作效率。数据源源不断推入FIFO,FIFO数据存满则自动将满标志置位,再通过INT8触发DM642的自动EDMA数据传输,这样可以在不占用CPU资源的情况下将FIFO数据传人DM642的内存(或外存)中指定的位置。数据积累到一定程度后,通过SEM标志通知网络发送程序,将该数据取走并进行网络发送。这种数据传输方法经过试验是可行的。因此整个程序按照功能大体分为3部分:初始化程序对硬件中断和网络进行了初始化和设置;EDMA中断程序中通知网络发送程序,该数据已经准备好;在网络发送程序中对数据进行打包发送,图4是各个部分的流程图。

图4 网络程序流程图

需要说明的是,在我们的设计之中,两个C6713 DSP是在DM642的指令下同时工作的,数据的发送也同步进行操作。DM642前端的两片FIFO并联构成了64位的数据宽度,每次EDMA读取的是64位数据,读人数据后再进行拆分、提取和打包发送。