2.2 开发中的一些问题

C6000系列属于高端DSP芯片,开发起来有一定的难度。在开发过程中难免遇到很多的困难和问题,下面就其中一些问题及解决办法加以讨论。

2.2.1 程序初始化问题

C6000 DSP程序的开发最好在TI提供的例子程序基础上进行相应的修改,这样不仅方便快捷,也可以避免很多意想不到的问题。我们的DM642用户程序就以NDK的“client”例子为基础修改而得。其中程序的初始化主要在DM642的初始化程序dm642init.c中和主程序client.c的开头部分。在dm642init.c中,对缓存、网络物理地址等进行了初始化;而在client.c中,则是对中断、EDMA等进行初始化。

在dm642init.c中主要的初始化为以下几行语句:

- CSL_init(); //初始化芯片函数库

- CACHE_clean(CACHE_L2ALL,0,0);//清缓存

- CACHE setL2Mode(CACHE_128KCACHE);//将L2缓存设为128K

- CACHE_enableCaching(CACHE_EMIFA_CE00);//允许外存CEOO作为缓存

- CACHE_enableCaching(CACHE_EMIFA_CE01);//允许外存CE01作为缓存

- //Init the EVM

- //EVMDM642_init();

- //EVMDM642_LED_init();

L2缓存即为DM642的内部RAM,大小共256k,既可以设为缓存也可以设为内存。网络收发数据需要至少开辟64k的缓存,缓存越大性能越好。由于程序还要使用一部分内存,因此以设128k缓存为宜。

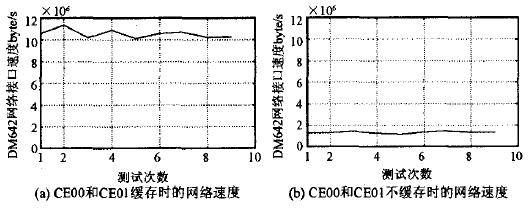

CACHE_enableCaching (CACHE_EMIFA_CE00)和CACHE_enableCaching(CACHE_EMIFA_CE01)的作用是开辟外存空间作为缓存,CE00对应外部RAM 的0x80000000~0x80FFFFFF空间,而CE01对应外部RAM 的0x81000000~0x81FFFFFF空间。在我们的开发板上的实践证明,这两个函数是必须的,如果不用,网络的性能要受到很大影响。实测数据如图5所示。

图5 CE00和CE01是否缓存对网络速度的影响

最后两个函数EVMDM642_LED_init()和EVMDM642_init()只适用于DM642EVM板,与板上的FPGA有关,而该FPGA的内部逻辑没有公开,所以在我们的开发板上这两个函数不能够正确运行。实践证明,在开发板上去掉这两个函数对程序性能影响不大。

在主程序client.c中,主要对中断、EDMA的通道等进行初始化。

- EMIFA_config(&emifaCfg0); //设置EMW

- IRQ_reset(IRQ_EVT_EDMAINT);//复位IRQ

- IER=0x303; //设置中断寄存器

- EDMA_config(hEdmaCha5,&edmaCfg0);//设置EDMA

- IRQ_enable(IRQ_EVT_EDMAINT);//允许IRQ

- HWI_enable(); //开硬件中断

- EDMA_intEnable(2); //允许EDMA中断

- EDMA_enableChannel(hEdmaCha5);//允许EDMA通道5

值得特别注意的是,DM642的网络发送之后,需要重新将缓存初始化,否则下一次接收时就会有个别数据出错。具体原因有待研究。即将以下语句写入到网络发送程序之后:

- CACHE_clean(CACHE_L2ALL,0,0);

- CACHE_setL2Mode(CACHE_128KCACHE);

- CACHE_enableCaching(CACHE_EMIFA_CE00);

- CACHE_enableCaching(CACHE_EMIFA_CE01);

2.2.2 硬件中断对网络程序的影响

以太网协议属于非实时网络协议,其内部实现机制也比较复杂。TI的NDK开发包中提供了符合berkeley socket标准的网络函数,如socket(),listen(),accept(),send(),recv()等等,但其内部源代码是不公开的。在实践中,我们遇到的一个较为突出的问题是,在数据量较大的情况下,FIFO的中断次数如果太频繁,会影响到DM642的网络发送。具体表现为程序运行并非十分平稳,中断较为频繁的时候,网络发送函数send()有时就会报错,返回(-1),导致该帧数据发送失败。

如果数据量较大且对数据信号处理实时性要求较高,那么该问题就会比较棘手,目前我们还未能够完全解决。但根据目前我们的需要,可以将网络发送的间隔时间延长。每次FIFO数据存满后,通过EDMA传输到外存中,但却不是每次存满都进行网络发送。而是将数据累积起来,多次的传输数据一起发送。这样的网络发送出错率会小得多。在软件编程上,也可以考虑双buffer甚至3个buffer的方式。一个buffer满后,进行发送,而此时的FIFO数据导入另外的buffer中,如此循环。另外软件上还需考虑容错机制,一次数据发送失败后,需要将该数据包重新发送,从而保证不丢失数据。事实上,以太网的速度是很快的,如图5所示,目前的DM642的网络接口我们实测的速度可以达到10-11 Mbyte/S(百兆网即100 Mbit/s,换算成字节大约11~12Mbyte/s)。需要指出的是,同样的数据流量条件下,大量的数据集合到一起一次发送,相比与分多次发送少量数据,要稳定得多。目前我们可以做到3 S发送一次,每次发送约5M 数据的较为稳定地程序运行,相信经过改进,还有较大的提高空间。

2.2.3 其它常见问题

参考文献[1]P44上提供了常见问题的列表,比如调用fdOpenSession()和fdCloseSession()的问题,PRD函数中设置100 ms周期的问题,内存溢出问题(设置“SO_LINGER”选项)等等,以及其他文献[5]上提到的“dispatcher选项”问题,上述问题笔者在实践中均遇到了,因此仔细阅读文献资料可以少走弯路。

3 结论

C6000系列DSP速度快,性能好,稳定性高,可以满足很多大规模信号处理系统的要求,但开发的难度也相对较大。我们完成的这一套信号处理-网络传输系统,FIFO和网络的数据传输是开发过程中遇到困难较多的一部分,其中一些问题仍需要深入探讨。目前,信号出口采用以太网,已经成为很多嵌入式系统的选择,形成一种趋势。随着网络技术和计算机集群技术的不断发展,从嵌入式网络接口输出的数据,可以通过网络接入到计算机集群中,进行更大规模的信号处理,这将是本文后续将要进行的工作。

参考文献:

[1] Texas Instruments TMS320C6000 TCP/IP Network Developer's Kit User's Guide.Texas Instruments,12-jun-2003.

[2] TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor Data Manual.Texas Instruments,August-2004.

[3] IDT 3.3 VOLT HIGH-DENSITY SUPERSYNC II NARROW BUS FIFO. IDT (Integrated Device Technology,Inc.Septemher-2003.

[4] Texas Instruments TMS320C6000 TCP/IP Network Developers Kit Programmers Reference Guide.Texas Instruments,12-Jun-2003.

[5] 李方慧等.TMS320C6000系列DSPs原理与应用(第二版) [M].电子工业出版社,2003