(3) 生成预期的输出响应

由于系统时钟为50MHz,要分频实现1Hz时钟波形过长,因此,下面以sec_1.vhd为例介绍仿真。

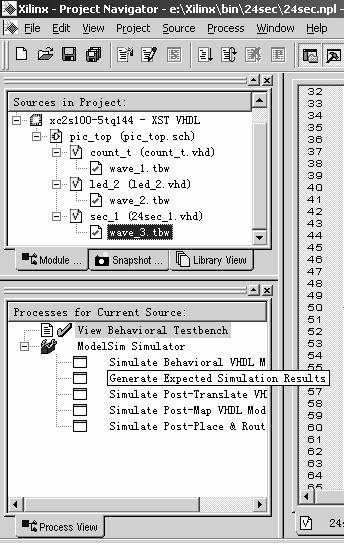

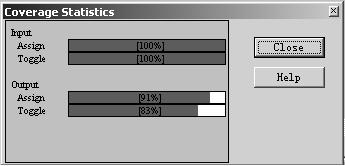

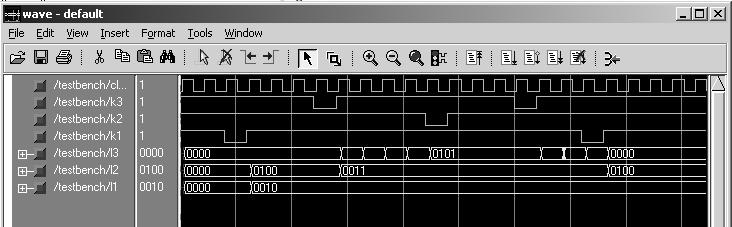

选择对应sec_1.vhd的仿真波形文件wave_3.tbw,执行Generate Expected Simulation Results操作(如图4.40所示),即可得到预期的输出响应波形(如图4.41所示),从图中可以看出,输出响应的波形满足设计要求。点击![]() ,可查看测试激励的覆盖率(如图4.42所示)。

,可查看测试激励的覆盖率(如图4.42所示)。

图4.40 生成预期的输出响应操作示意图

图4.41 生成预期的输出响应

图4.42 测试激励的覆盖率示意图

(4)使用ModelSim进行仿真

根据HDL Bencher中产生的预期结果,接着就可以使用Modelsim进行仿真(Simulate)Modelsim进行仿真可分为行为仿真(亦即功能仿真)和布局布线后仿真(时序仿真)。

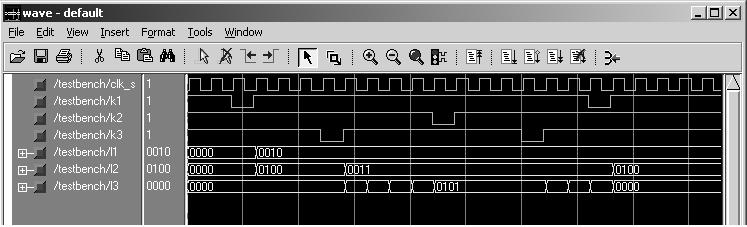

我们先进行行为仿真。选择wave_3.tbw,执行Simulate Behavioral VHDL Model(行为仿真)操作(如图4.43所示),可得到如图4.44所示的行为仿真结果,从仿真波形可以看出,仿真结果是正确的。仿真完后关闭Modelsim主窗口退出Modelsim。

图4.43 行为仿真操作示意图

图4.44 行为仿真波形图

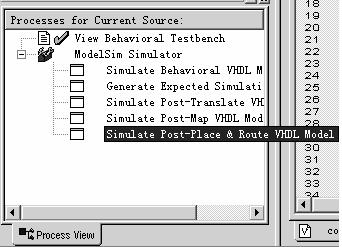

再进行时序仿真:选择wave_3.tbw,执行Simulate Post-Place & Route VHDL Model(布局布线后仿真,即时序仿真)操作(如图4.45所示),可得到如图4.46所示的时序仿真结果,从仿真波形可以看出,仿真结果是正确的,并且从输入到产生输出,有一定的时间延迟。仿真完后关闭Modelsim主窗口退出Modelsim。

图4.45 时序仿真操作示意图

图4.46 时序仿真波形图

依照上述的操作步骤,分别对其他程序进行有关的仿真及分析。

5)建立和编辑顶层原理图文件

对于顶层文件,即可使用VHDL文本输入方式,也可使用原理图输入方式。这里我们将使用原理图的输入方式来建立顶层文件。

(1)原理图形符号的生成(Symbol)

为了在原理图的设计中利用前面已使用VHDL进行有关设计的成果,我们先要将经过编译后的VHDL程序生成可供原理图设计中直接调用的原理图形符号。

选择 count_t.vhd,执行Create Schematic Symbol操作(如图4.47所示),即可生成可供原理图设计中直接调用的原理图形符号count_t。同理,对其他两个文件执行相同的操作。

图4.47 原理图形符号的创建操作

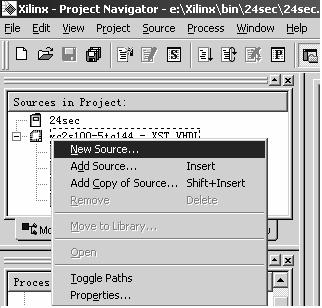

(2)顶层原理图文件的创建

选中工程,鼠标右点,在弹出的窗口中选择New Source(如图4.48所示) ,再在弹出的窗口中选择文件的类型为Schematic,并输入文件名pic_top后,执行”下一步”,即完成了原理图文件的创建,进入原理图的编辑状态。

图4.48 原理图的创建操作

(3)原理图的编辑

① 放置元件(Symbols):在Symbols 的e:/xilinx/bin/24sec中选中所需元件的原理图符号,并在右边的图中期望的位置点左键进行放置,如图4.49所示。若位置不合适,可进行移动调整。

图4.49 在原理图中放置元件的操作

② 元件间的连线:点![]() ,进行连线操作。

,进行连线操作。

③ 放置I/O端口并编辑端口名:点![]() ,放置I/O端口。选中端口,点右键,在弹出的对话框中选择“Rename Port”后,再在弹出的对话框中输入系统设定的端口名。或者双击端口,在弹出的对话框中输入系统设定的端口名。

,放置I/O端口。选中端口,点右键,在弹出的对话框中选择“Rename Port”后,再在弹出的对话框中输入系统设定的端口名。或者双击端口,在弹出的对话框中输入系统设定的端口名。

④ 原理图的保存:原理图编辑好后(如图4.50所示),应执行存盘操作,将原理图进行保存。

图4.50 编辑好的顶层原理图

⑤ 原理图错误的检查:为了检查原理图是否有错,可执行原理图的检错操作。若有错,则改正,直到完全正确为止。

⑥ 原理图的逻辑综合:若原理图经过检查没有错误,可进行逻辑综合。

| 网站导航: 首页 > 设计参考 > 正文 | 文章搜索 |